1. 环境结构

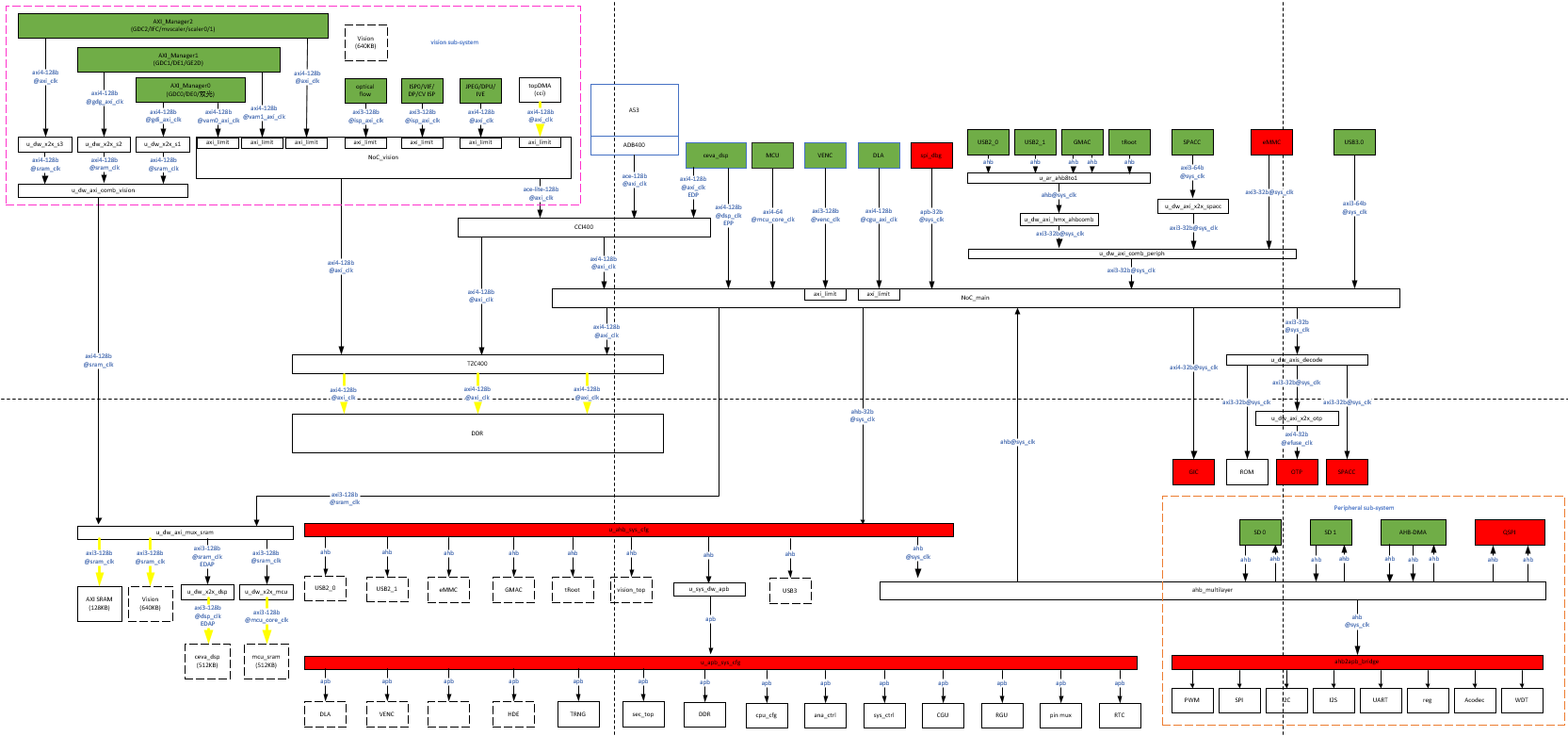

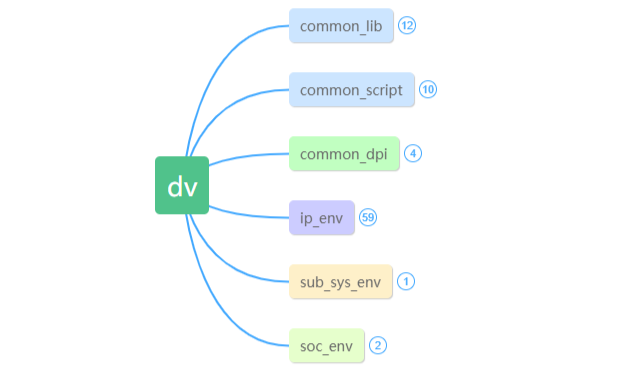

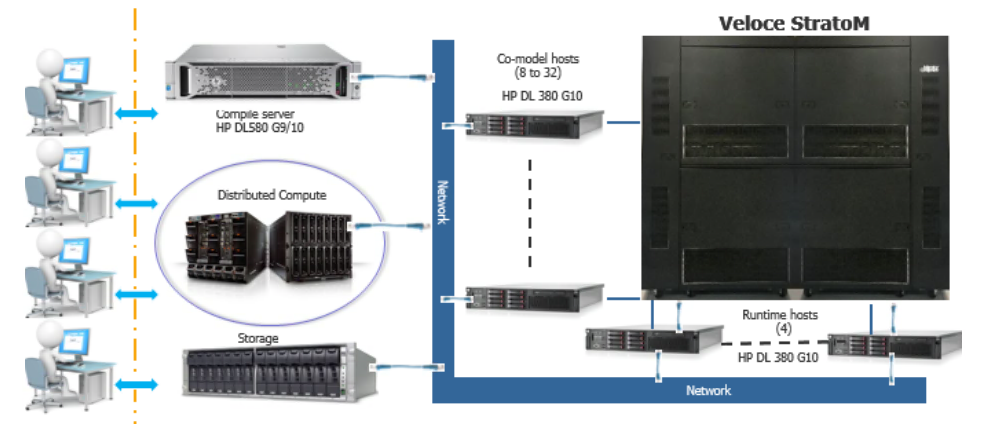

基于西门子Veloce的UVM硬件加速验证平台,其主要覆盖IP仿真加速,SOC系统验证,应用场景功耗分析等几个方面。验证环境采用的目录结构与pioneer #1保持一致。

采用硬件加速之后,DUT运行的时间极大的缩短,相比较与VCS仿真,可提高运行速度120倍左右。

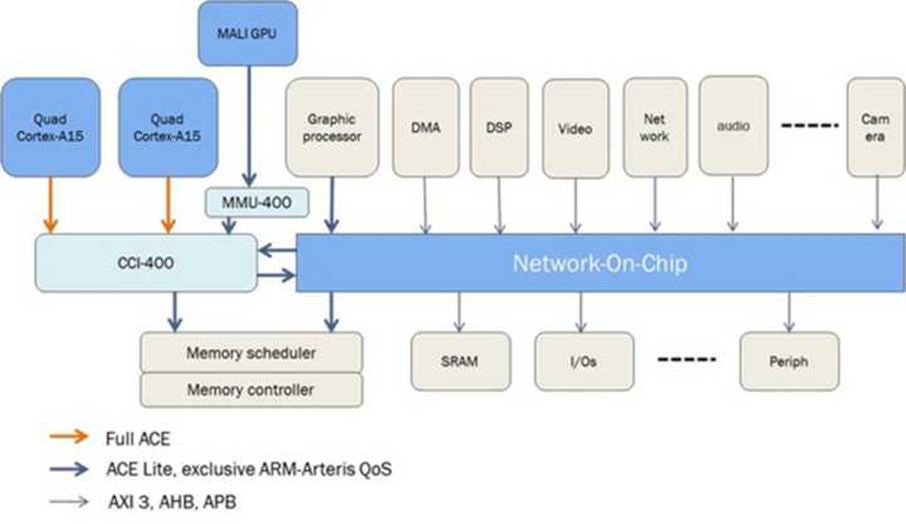

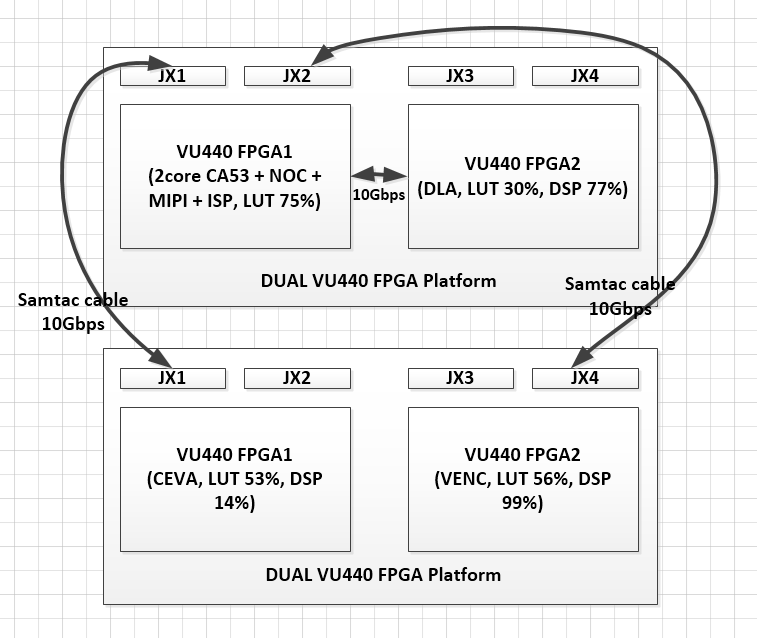

Veloce硬件平台的结构如图所示。

1.1 设计思想

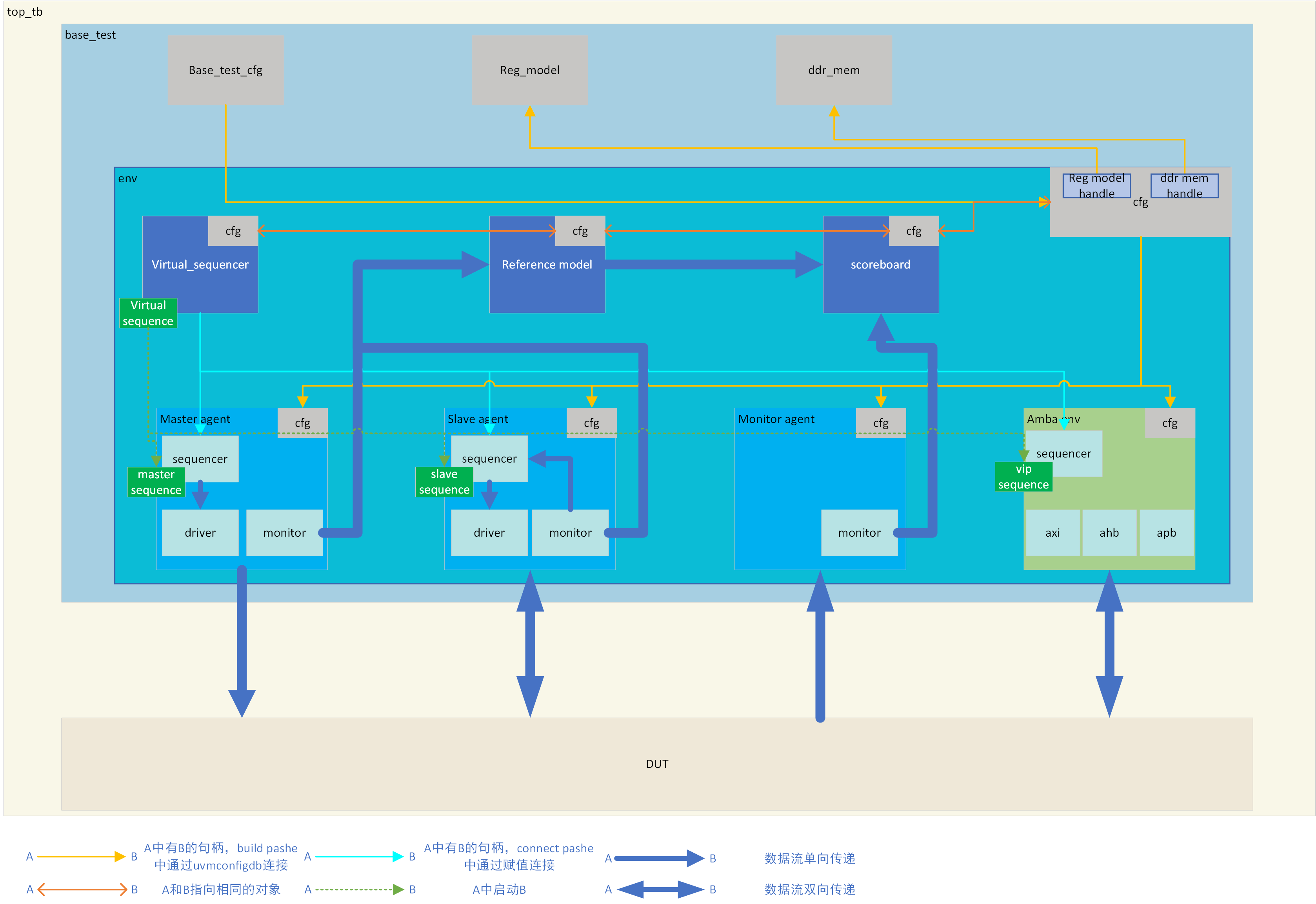

硬件加速验证就是将DUT代码完全在veloce平台上运行起来,针对UVM环境做一些特定的修改,实现流程如下:

修改ASIC设计(时钟,复位,memory,PHY,PAD)

将UVM环境分割成HVL和HDL两个部分

使用Transaction Library进行HVL和HDL的通信

采用veloce综合,加速仿真