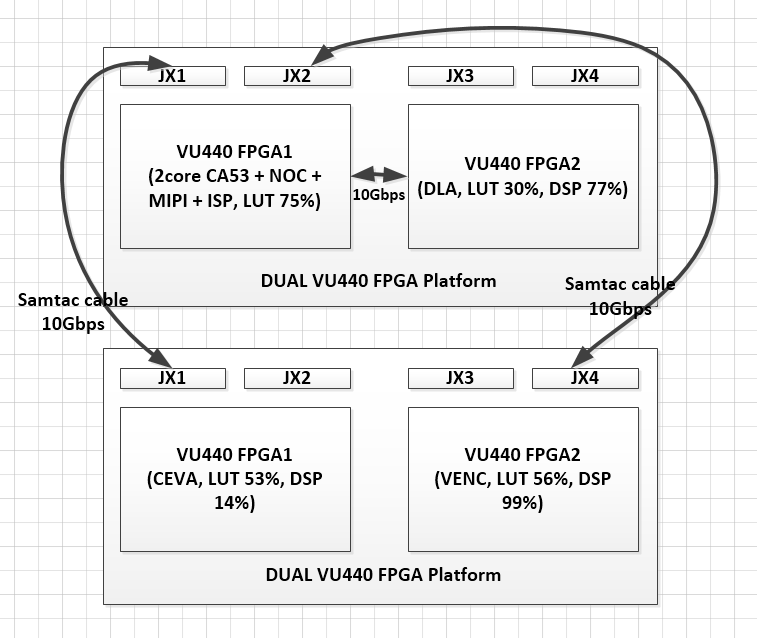

Prototype Example

如下图所示,对于大型ASIC芯片原型验证,采用4颗VU440级联,使用高速serdes接口和线缆进行连接,在RTL层面完成多芯片的分割与互连。

<<– RTL modify –>>

1,时钟树上的mux,调用common 目录下的 clock_mux.v。在clock_mux.v中统一定义 XILIXN_FPGA 宏,调用BUFGMUX原语。

2,非时钟树上的mux,调用common目录下的func_mux.v。

3,如果定义了”XXX_TOP_DUMMY” 或者 “XXX_OFF”宏,需要在宏里面将所有的output信号tie 0/1,不能悬空。

4,所有asic memory的调用,遵从命名格式,由脚本会统一生成fpga所需要的memory。

5,所有analog model的调用,添加 “XILINX_FPGA” 宏,并在宏里面完成可综合的rtl逻辑。

6,PIN SHARE相关代码添加 “NON_PIN_SHARE” 宏的相关去除逻辑。

7,按照fpga分割要求,创建top_f1.v,top_f2.v, top_f3.v,top_f4.v,创建serdes互连相关文件,加入aurora_64b66b仿真文件列表。

<<– VCS simulation –>>

1,修改rtl_fpga.f,去除stdcell_tsmc.f,io_model.f,mem_model_ip.f,design_ware.f,ddr_rtl.f。

2,添加fpga ddr 仿真model,fpga仿真model,模拟ip仿真model,vivado clock wizard仿真model。

3,添加xilinx标准库。

4,编译cpu firmware,关闭firmware中ddr_init相关代码,将bl1.bin转换成code.hex,初始化进fpga rom仿真model中。

5,修改tb.sv,添加uart的真实rx,初始化PTCM, DTCM。

6,在tb.sv中例化top_f1, top_f2, top_f3, top_f4,例化serdes接口进行连接,注意按照fpga的实际连接方式,serdes连接要有反向映射关系。

7,对IP生成的模型,执行convert脚本生成ddr初始化相关hex文件,初始化进ddr model中。

8,make com编译,make elab生成work库,make sim仿真。

<<– Synplify synthesis –>>

1,自底向上方法创建单个module的filelist,prj文件,sdc文件。在综合选项中设置 -fix_gated_and_generated_clocks 1 和 -force_async_genclk_conv 1 会自动转换门控时钟。

2,调用run.py脚本,自底向上执行,会自动解析filelist,自动生成工程文件。

3,执行脚本check_gated_clock.sh检查所有log,确保gated clock全部被转换成功。

4,针对需要添加probe的模块,创建fdc约束,重新综合。

<<– Vivado implement –>>

1,采用vivado tcl模式,创建工程目录,编写工程脚本。

2,生成fpga平台对应的DDR controller和相关时钟 clock wizard,SRAM,等IP。

3,vivado是时序驱动的,所以完备的sdc文件非常重要。针对速度相对高的IO接口,可采用虚拟时钟约束。

4,VU440和VU19P平台均包括多个DIE,xilinx称为SLR。对于跨SLR的模块,时序上较难满足,可以使用Pblock限制模块不要跨SLR。

5,例化ILA core,添加相关的敏感信号,便于上板调试。

6,布局布线完成后,通过ECO模式,打开相应的dcp文件,做ECO操作,可快速生成新的bitfile。

7,如果新的设计只有少量修改,在时序满足的情况下,可使用增量综合模式,减少布局布线时间。

<<– Hardware debug –>>

1,FPGA平台启动成功后,可通过JTAG连接的方式读取状态调试。

2,CPU如果能正常启动Uboot,可方便的调试外设。

3,内部逻辑信号可以通过Vivado Lab连接硬件平台,读取内部逻辑的波形。