1. 环境结构

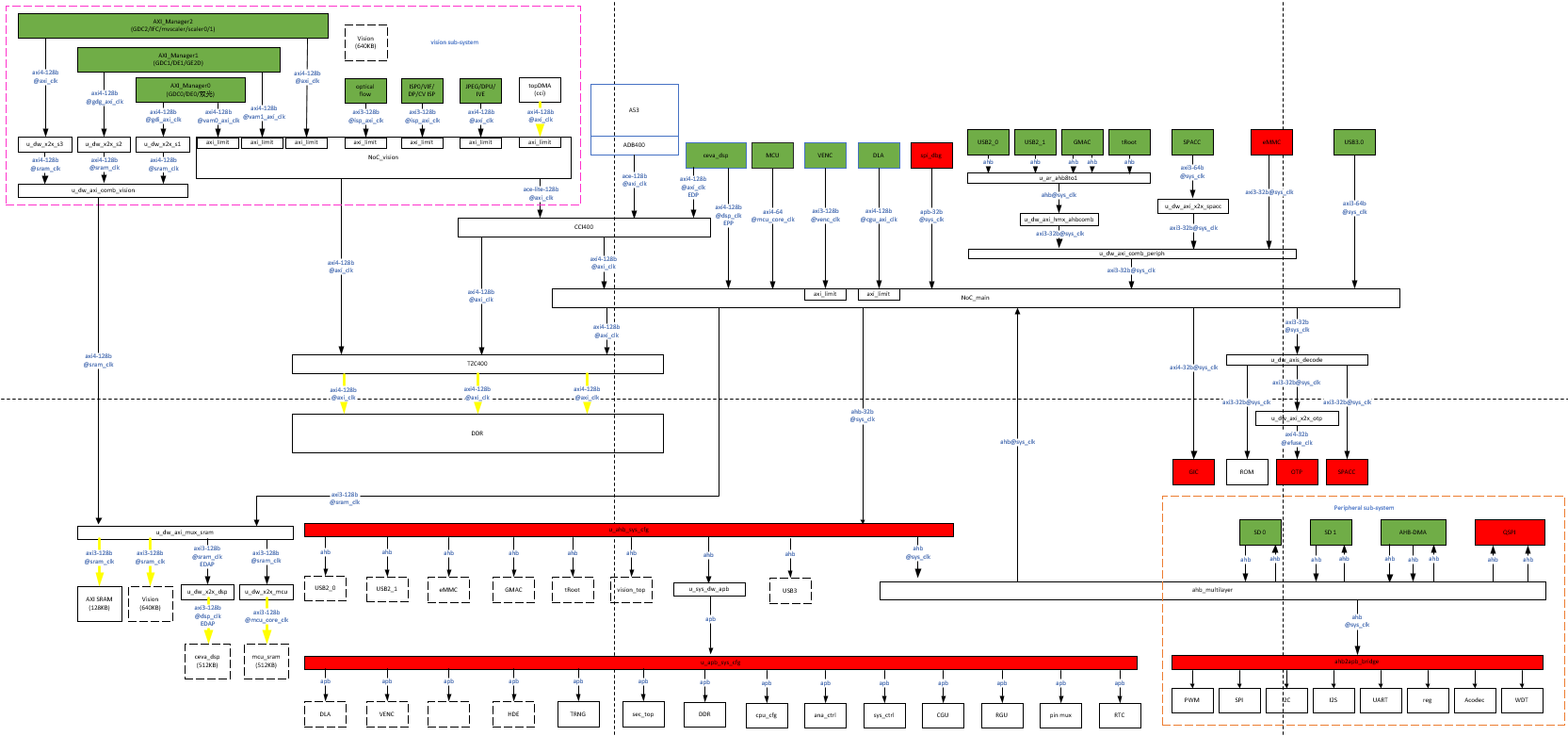

总线验证的UVM环境结构与Pioneer #1的通用结构保持一致,例化整个SOC作为DUT,在需要测试的总线接口处采用force语句加入amba vip的master和slave,同时也可以全部连接DUT,使用真实的CPU控制各个IP正常工作。

1.1 设计思想

为有效的验证总线功能与性能,采取如下策略:将绿色模块替换amba vip,将黄色的接口连接amba monitor ,白色模块(A53,DMA,DDR,SRAM以及所有的slave)采用真实的RTL,红色模块不参与测试。

功能测试场景如下:

A53中运行firmware,做DMA数据搬运,同时开启所有的amba master vip,随机访问DDR和SRAM空间的不同地址区域,并做数据比对。

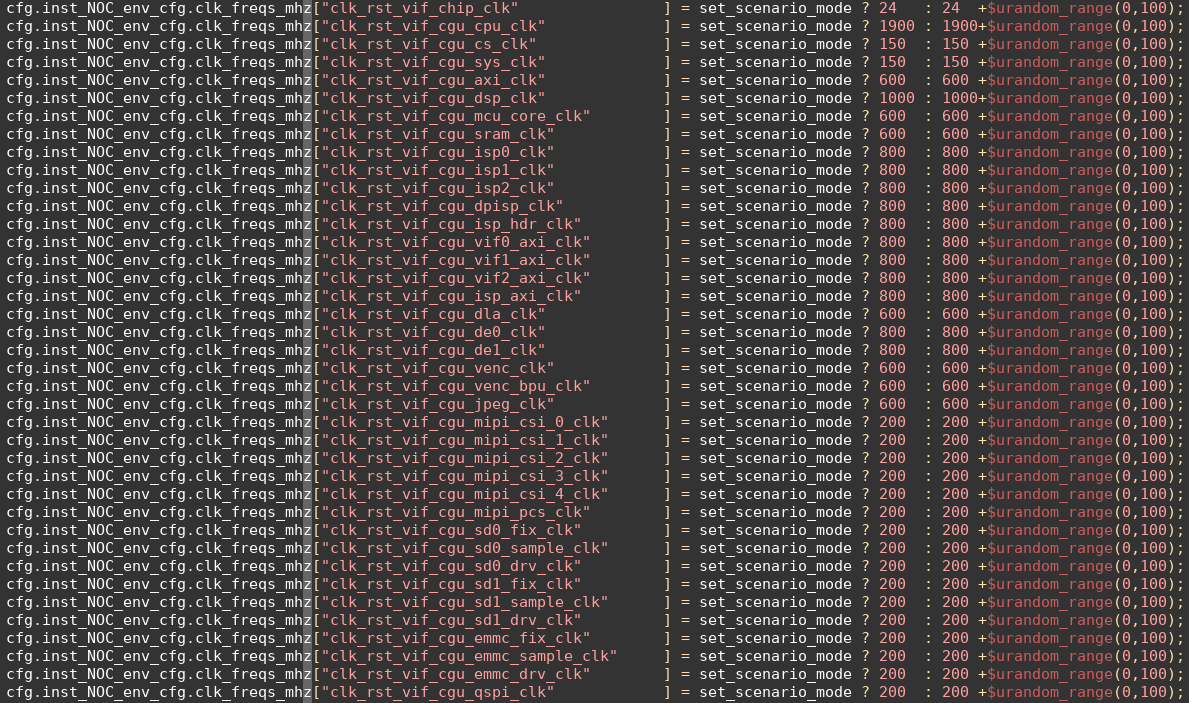

NOTE:在功能测试中,将所有时钟设置成随机频率,模拟异步的时钟关系。

性能测试场景如下:

NOTE:在性能测试中,将所有时钟设置成signoff频率。

1.2 实现方式

使用Pioneer #1工具自动化生成UVM基本框架,使用脚本如下:

./dvgen.py -e NOC -p Kuiper -soc -has_amba -uvm

在top_tb.sv中例化所需要的所有时钟接口,并force到CGU输出端口上。

在top_tb.sv中例化所需要的所有总线接口,并force到IP的输出端口上。

- axi_if.master_if[ 0] 对应NOC_MAIN的VENC接口,分配DDR地址32’h2001_0000,SRAM地址32’h0060_0000

- axi_if.master_if[ 1] 对应NOC_MAIN的DLA接口,分配DDR地址32’h2401_0000,SRAM地址32’h0061_0000

- axi_if.master_if[ 2] 对应NOC_MAIN的MCU接口,分配DDR地址32’h2801_0000,SRAM地址32’h0062_0000

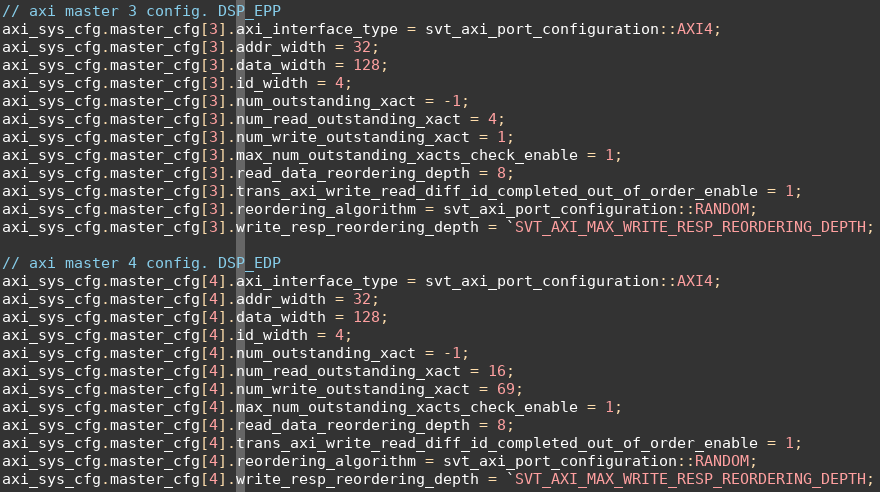

- axi_if.master_if[ 3] 对应NOC_MAIN的DSP(EPP)接口,分配DDR地址32’h2c01_0000,SRAM地址32’h0063_0000

- axi_if.master_if[ 4] 对应NOC_MAIN的DSP(EDP)接口,分配DDR地址32’h3001_0000,SRAM地址32’h0064_0000

- axi_if.master_if[ 5] 对应NOC_MAIN的SPACC接口,分配DDR地址32’h3401_0000,SRAM地址32’h0065_0000

- axi_if.master_if[ 6] 对应axi_comb_vision的GDC_RSZ_IFC_SRAM接口,分配SRAM地址32’h0066_0000

- axi_if.master_if[ 7] 对应NOC_MAIN的USB3接口,分配DDR地址32’h3801_0000,SRAM地址32’h0067_0000

- axi_if.master_if[ 8] 对应NOC_VISION的ISP_SUB_TOP接口,分配DDR地址32’h3c01_0000F,SRAM地址32’h0068_0000

- axi_if.master_if[ 9] 对应NOC_VISION的GDC_DE_INF接口,分配DDR地址32’h4001_0000,SRAM地址32’h0069_0000

- axi_if.master_if[10] 对应NOC_VISION的GDC_DE_GED接口,分配DDR地址32’h4401_0000,SRAM地址32’h006a_0000

- axi_if.master_if[11] 对应NOC_VISION的GDC_RSZ_IFC接口, 分配DDR地址32’h4801_0000,SRAM地址32’h006b_0000

- axi_if.master_if[12] 对应NOC_VISION的JPG_IVE_DPU接口,分配DDR地址32’h4c01_0000,SRAM地址32’h006c_0000

- axi_if.master_if[13] 对应NOC_VISION上的OPTICAL接口,分配DDR地址32’h5001_0000,SRAM地址32’h006d_0000

- axi_if.master_if[14] 对应axi_comb_vision上的GDC_DE_INF_SRAM接口,分配SRAM地址32’h006e_0000

- axi_if.master_if[15] 对应axi_comb_vision上的GDC_DE_GED_SRAM接口,分配SRAM地址32’h006f_0000

- ahb_if.master_if[ 0] 对应NOC_MAIN上AXI_COMB的USB2_0,分配DDR地址起始32’hD000_0000,SRAM地址起始32’h0074_0000

- ahb_if.master_if[ 1] 对应NOC_MAIN上AXI_COMB的USB2_1,分配DDR地址起始32’hD100_0000,SRAM地址起始32’h0076_0000

- ahb_if.master_if[ 2] 对应NOC_MAIN上AXI_COMB的GMAC_TX,分配DDR地址起始32’hD200_0000,SRAM地址起始32’h0078_0000

- ahb_if.master_if[ 3] 对应NOC_MAIN上AXI_COMB的GMAC_TX,分配DDR地址起始32’hD300_0000,SRAM地址起始32’h007C_0000

- ahb_if.master_if[ 4] 对应NOC_MAIN上AXI_COMB的TROOT,分配DDR地址起始32’hD400_0000,SRAM地址起始32’h007F_0000

- ahb_if.master_if[ 5] 对应NOC_MAIN上AHB_Multilayer的SD_0,分配DDR地址起始32’hD500_0000,SRAM地址起始32’h0081_0000

- ahb_if.master_if[ 6] 对应NOC_MAIN上AHB_Multilayer的SD_1,分配DDR地址起始32’hD600_0000,SRAM地址起始32’h0083_0000

- ahb_if.master_if[ 7] 对应NOC_MAIN上AHB_Multilayer的DMA0,分配DDR地址起始32’hD700_0000,SRAM地址起始32’h0085_0000

- ahb_if.master_if[ 8] 对应NOC_MAIN上AHB_Multilayer的DMA0,分配DDR地址起始32’hD800_0000,SRAM地址起始32’h0087_0000

创建各个slave总线接口,并force到需要监测的端口,并配置slave为passive模式,只做monitor统计带宽和延时:

- axi_if.slave_if[ 0] 对应DDR_TOP的axi接口0,配置成passive模式

- axi_if.slave_if[ 1] 对应DDR_TOP的axi接口1,配置成passive模式

- axi_if.slave_if[ 2] 对应DDR_TOP的axi接口2,配置成passive模式

- axi_if.slave_if[ 3] 对应SRAM_TOP的axi_sram接口,配置成passive模式

- axi_if.slave_if[ 4] 对应VISION_TOP的srammux_to_visionsram接口,配置成passive模式

- axi_if.slave_if[ 5] 对应DSP_TOP的cevaxm6_edap接口,配置成passive模式

所有总线上的master和slave端口的协议类型,数据位宽,地址位宽,ID位宽,支持outstanding能力,是否支持out of order,性能的统计间隔,性能统计的最大最小值等等配置都在[NOC_cust_svt_amba_system_configuration.sv]中。

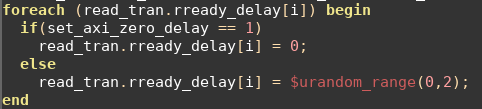

AXI Master读写delay控制有两种模式:默认情况读写delay平均有1个cycle;zero delay模式下,master没有反压。

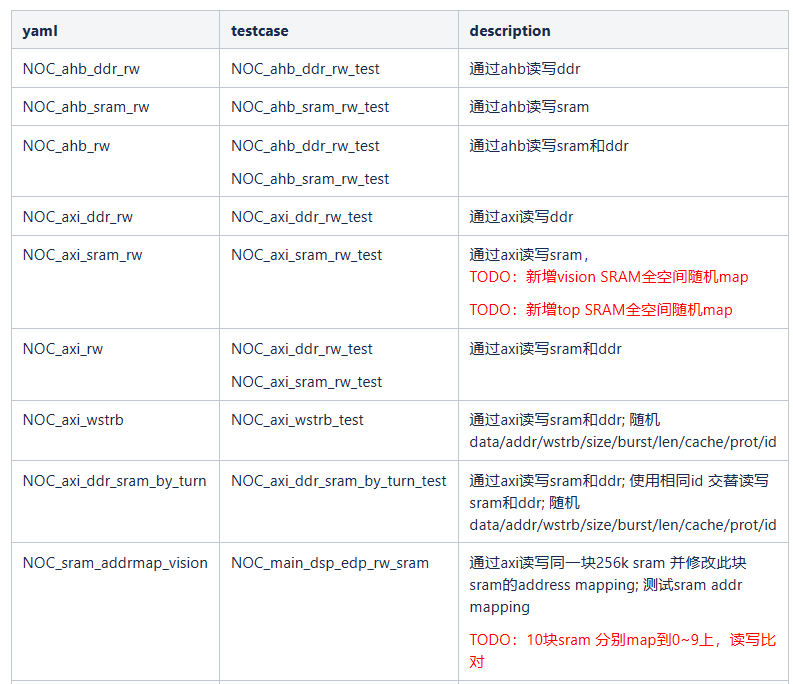

1.3 Test Point

1.4 使用方法

运行方式如下。脚本具体使用方法参照《Pioneer #1 验证白皮书》的章节5:Sim_Tool介绍 Pioneer #1 验证白皮书

特别注意:使用micron的ddr4仿真模型时,在vcs编译选项中不能添加 +vcs+initmem+random 命令行参数,这个参数会导致ddr4仿真模型会随机性的工作不正常,DQS的read preamble偶尔消失。

RTL仿真环境使用如下:

1 | $ cd sim && source SourceMe |

DC网表仿真环境使用如下:

1 | $ cd sim\_dc\_netlist && source SourceMe |

PR网表仿真环境使用如下:

1 | $ cd sim\_pr\_netlist && source SourceMe |

2. 验证结果分析

结果分析主要包含功能点检查和性能报告与功耗报告,其中由脚本自动抓取log生成相关的报告。

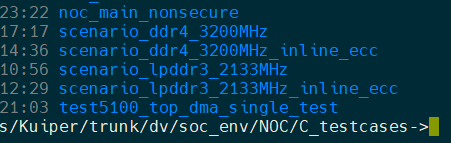

针对ddr的初始化,主要使用如上所示firmware,其中noc_main_nonsecure,test5100_top_dma_single_test用作功能测试;scenario_xxx用作性能测试(ddr4,lpddr3,ecc on/off)。

2.1 功能报告

| master | slave | 读写数据一致性 | AW_LEN/AR_LEN | AW_SIZE/AR_SIZE | AW_BURST/AR_BURST | AWPROT/ARPROT | AWCACHE/ARCACHE | WSTRB |

|---|---|---|---|---|---|---|---|---|

| VENC | ddr | pass | 2/4/8 | 4 | INCR | 0 | 0 | FFFF |

| sram | pass | 2/4/8 | 4 | INCR | 0 | 0 | FFFF | |

| random | pass | 2/4/8 TODO: 1-16 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| DLA | ddr | pass | 1-16 | 4 | INCR | 0 | 0 | FFFF |

| sram | pass | 1-16 | 4 | INCR | 0 | 0 | FFFF | |

| random | pass | 1-16 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| MCU | ddr | pass | 1/8 | 3 | INCR/WRAP8 | 0 | 0 | FF |

| sram | pass | 1/8 | 3 | INCR/WRAP8 | 0 | 0 | FF | |

| random | pass | 1/8 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| DSP EPP | ddr | pass | 1 | 4 | INCR/WRAP2/WRAP4/WRAP8/WRAP16 | 0 | 0 | FFFF |

| sram | pass | 1 | 4 | INCR/WRAP2/WRAP4/WRAP8/WRAP16 | 0 | 0 | FFFF | |

| random | pass | 1 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| DSP EDP | ddr | pass | 1-256 | 4 | INCR | 0 | 0 | FFFF |

| sram | pass | 1-256 | 4 | INCR | 0 | 0 | FFFF | |

| random | pass | 1-256 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| SPACC | ddr | pass | 1-16 | 3 | INCR | 0 | 0 | FF |

| sram | pass | 1-16 | 3 | INCR | 0 | 0 | FF | |

| random | pass | 1-16 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| GDC_RSZ_IFC_SRAM | sram | pass | 8 | 4 | INCR | 0 | 0 | FFFF |

| random | pass | 8 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| USB3 | ddr | pass | 1-16 | 3 | INCR | 0 | 0 | FF |

| sram | pass | 1-16 | 3 | INCR | 0 | 0 | FF | |

| random | pass | 1-16 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| ISP_SUB_TOP | ddr | pass | 1-16 | 4 | INCR | 0 | 0 | FFFF |

| random | pass | 1-16 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| GDC_DE_INF | ddr | pass | 1-17 | 4 | INCR | 0 | 0 | FFFF |

| sram | pass | 1-17 | 4 | INCR | 0 | 0 | FFFF | |

| random | pass | 1-17 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| GDC_DE_GED | ddr | pass | 1-17 | 4 | INCR | 0 | 0 | FFFF |

| sram | pass | 1-17 | 4 | INCR | 0 | 0 | FFFF | |

| random | pass | 1-17 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| GDC_RSZ_IFC | ddr | pass | 1-17 | 4 | INCR | 0 | 0 | FFFF |

| sram | pass | 1-17 | 4 | INCR | 0 | 0 | FFFF | |

| random | pass | 1-17 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| JPG_IVE_DPU | ddr | pass | 1-16 | 4 | INCR | 0 | 0 | FFFF |

| sram | pass | 1-16 | 4 | INCR | 0 | 0 | FFFF | |

| random | pass | 1-16 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| OPTICAL | ddr | pass | 1-16 | 4 | INCR | 0 | 0 | FFFF |

| random | pass | 1-16 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| GDC_DE_INF_SRAM | sram | pass | 8 | 4 | INCR | 0 | 0 | FFFF |

| random | pass | 8 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| GDC_DE_GED_SRAM | sram | pass | 8 | 4 | INCR | 0 | 0 | FFFF |

| random | pass | 8 | RANDOM | INCR | RANDOM | RANDOM | RANDOM | |

| USB2_0 | ddr | pass | 1-16 | RANDOM | INCR | 0 | ||

| sram | pass | 1-16 | RANDOM | INCR | 0 | |||

| random | pass | 1-16 | RANDOM | INCR | 0 | |||

| USB2_1 | ddr | pass | 1-16 | RANDOM | INCR | 0 | ||

| sram | pass | 1-16 | RANDOM | INCR | 0 | |||

| random | pass | 1-16 | RANDOM | INCR | 0 | |||

| GMAC_TX | ddr | pass | 1-16 | RANDOM | INCR | 0 | ||

| sram | pass | 1-16 | RANDOM | INCR | 0 | |||

| random | pass | 1-16 | RANDOM | INCR | 0 | |||

| GMAC_RX | ddr | pass | 1-16 | RANDOM | INCR | 0 | ||

| sram | pass | 1-16 | RANDOM | INCR | 0 | |||

| random | pass | 1-16 | RANDOM | INCR | 0 | |||

| TROOT | ddr | pass | 1-16 | RANDOM | INCR | 0 | ||

| sram | pass | 1-16 | RANDOM | INCR | 0 | |||

| random | pass | 1-16 | RANDOM | INCR | 0 | |||

| SDCARD0 | ddr | pass | 1-16 | RANDOM | INCR | 0 | ||

| sram | pass | 1-16 | RANDOM | INCR | 0 | |||

| random | pass | 1-16 | RANDOM | INCR | 0 | |||

| SDCARD1 | ddr | pass | 1-16 | RANDOM | INCR | 0 | ||

| sram | pass | 1-16 | RANDOM | INCR | 0 | |||

| random | pass | 1-16 | RANDOM | INCR | 0 | |||

| DMA0 | ddr | pass | 1-16 | RANDOM | INCR | 0 | ||

| sram | pass | 1-16 | RANDOM | INCR | 0 | |||

| random | pass | 1-16 | RANDOM | INCR | 0 | |||

| DMA1 | ddr | pass | 1-16 | RANDOM | INCR | 0 | ||

| sram | pass | 1-16 | RANDOM | INCR | 0 | |||

| random | pass | 1-16 | RANDOM | INCR | 0 |

2.2 性能报告

使用脚本gen_perf_report.py可以自动提取vcs_sim.log中的信息,并填写template excel文件中的绿色区域部分。使用参考示例如下:

1 | ./gen\_perf\_report.py ./out/cases/NOC\_test\_num1\_1\_num2\_1/ ../script/noc\_performance\_template.xlsx |

gen_perf_report.py脚本是自动匹配log文件中的关键字,提取出read throughput和write throughput信息,然后填表。在AMBA VIP performance的定义中,throughput是单位统计时间内传输的byte数,VIP报出来的throughput是经过换算后的,单位为MB/s。在AMBA VIP performance的定义中,bandwidth是单位统计时间内传输的byte数/延时,这个定义难以理解。在Pioneer #2中统计的带宽是VIP报出来的throughput信息。

gen_perf_report.py脚本中定义了4个字典保存基本信息,同时定义了2个变量来保存起始行和时间间隔字符串。

- id_name_dict_noc_master字典存放的是所有VIP master的ID,也就是对应AMBA configuration文件中的master[xx]

- id_name_dict_noc_slave字典存放的是所有VIP slave的ID,也就是对应AMBA configuration文件中的slave[xx]

- perf_indict_column_dict字典存放的是性能报告excel的相关列number,以及该列对应的performance信息(latency,throughput,efficiency)

- all_perf_ip_line_offset字典存放的是性能报告excel的相关行bumber,以及该行对应的master信息

- row_index对应的是从第几行开始填写性能报告表格

- time_region对应的是VIP time interval区间,需要与log中的信息完全对应

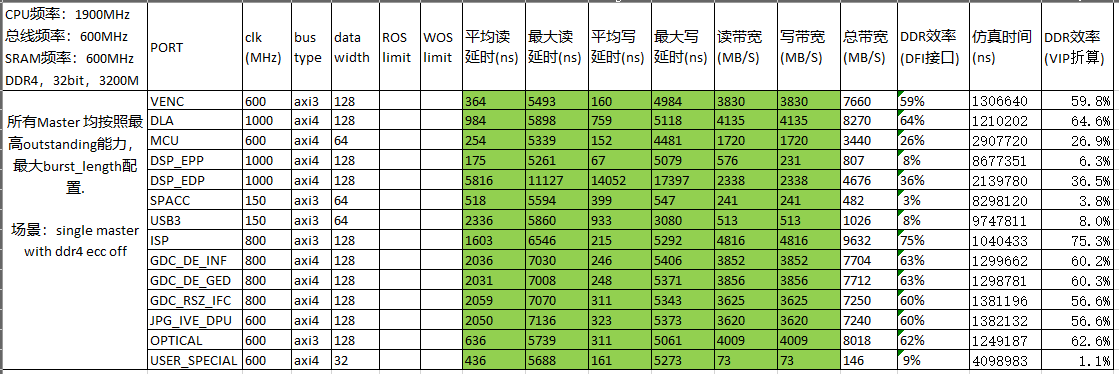

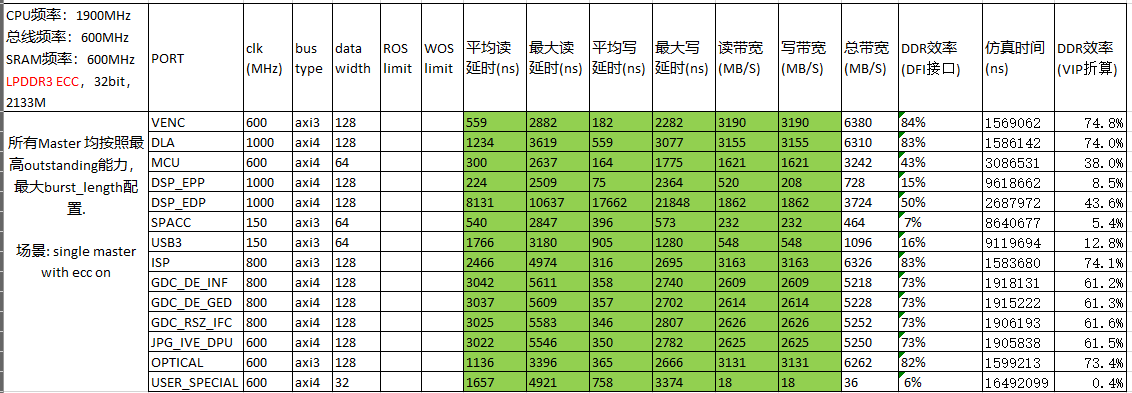

2.2.1 单master性能测试机制

每个master使用最高频率,最大burstlen,随机读写5000000 byte的数据,地址对齐16byte,递增。根据消耗的时间来折算每个master能得到的最大带宽。

单master性能(DDR4 ECC off,3200Mhz, 32bit)

单master性能(DDR4 ECC on,3200Mhz, 32bit)

单master性能(LPDDR3 ECC off,2133Mhz, 32bit)

单master性能(LPDDR3 ECC on,2133Mhz, 32bit)

2.2.2 多master性能测试机制

每个master使用最高频率,实际burstlen,实际outstanding,随机读写场景对应的10ms的数据。地址对齐16byte,递增。 QOS未限定。根据消耗的时间来折算每个master能得到的最大带宽。

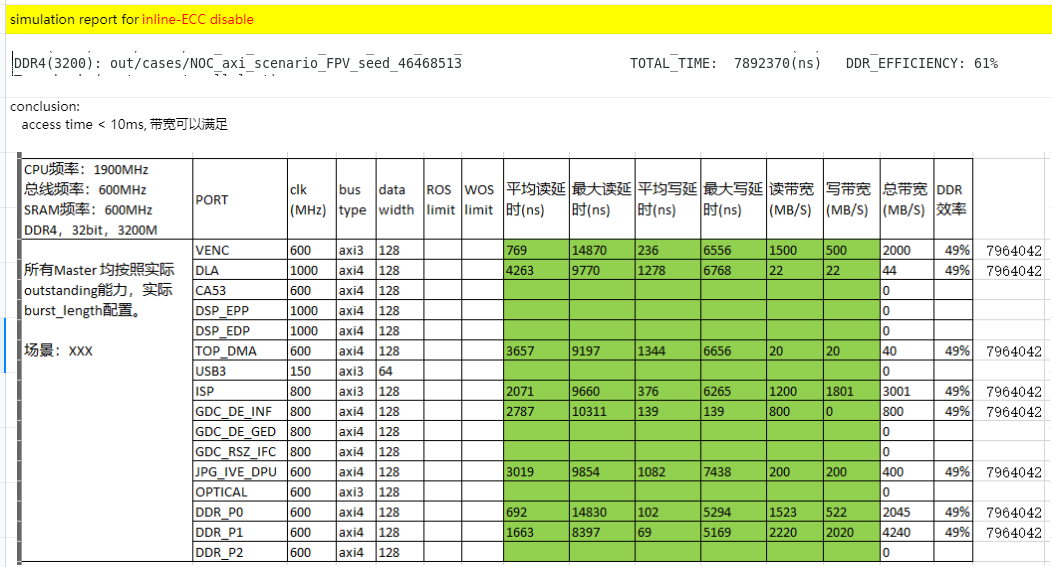

FPV场景性能(DDR4,32bit, 3200M, ECC off)

无人机5.4K30fps-zoom小于2场景性能(DDR4,32bit, 3200M, ECC off)

AR10非压缩场景性能(LPDDR3,32bit, 2133M, ECC off)

3. 功耗结果分析

基于RTL的功耗分析具有很大的不确定性,在Pioneer #2中,采用前端dc网表和后端pr网表来做功耗分析。

pt_power.xxx.tcl脚本是功耗分析脚本,供功耗分析工具PrimeTimePX使用,针对前端DC网表,功耗分析脚本需要输入DC网表,DC产生的SDC文件,基于前端DC网表的fsdb波形文件。针对后端PR网表,功耗分析脚本需要输入后端的PT session,基于后端PR网表的fsdb波形文件。设置合理的选项,即可得到合理的功耗数据。

set power_enable_advanced_fsdb_reader true可以避免fsdb版本不匹配的问题

set power_limit_extrapolation_range true可以限制PTPX对高负载模型的估算问题,针对前端DC网表,必须将这个变量设置为true

set power_use_ccsp_pin_capacitance true可以更精确的推算电容充放电功耗,建议设置为true

功耗分析工具PrimeTimePX将功耗分成以下三种:

Net Switching Power:cell外部的连线上RC充放电产生的功耗,主要是电压切换的过程中产生的,属于动态功耗

Cell Internal Power:cell内部的RC充放电产生的功耗,同时包括瞬时的短路功耗,也包括clock pin上的clock翻转功耗

Cell Leakage Power:所有cell的静态功耗,只要通电就会产生,与cell的阈值电压,工作温度和工艺corner有关

比较前端DC网表功耗和后端PR网表功耗结果可以看出:

Internal Power基本上一致,有大约10%的增幅,增幅原因在于后端团队在时序收敛过程中会增加额外的buffer;

Leakage Power有较大的增幅,增幅原因在于后端团队在实现过程中会采用不同阈值电压的cell来增大驱动能力或者收敛时序(LVT,SVT,HVT),同时额外增加的cell也会增大leakage,这里增幅大约150%;

Net Switching Power增幅最大,大约400%的增幅,主要原因在于后端PR网表附带了spef信息(SPEF是Standard Parasitic Extraction Format的缩写,用于描述芯片在PR之后实际电路中的 R L C 的值),能够描述连线的物理信息,充放电功耗更准确。

基于前端DC网表的功耗与后端PR网表的功耗分析结果,可以大致得出一个比例关系,即从前端DC网表的功耗推算出合理的后端PR网表功耗,进而在前期即可相对准确的评估总线和系统功耗。如下表所示,根据前端DC网表功耗,估算出后端PR网表的功耗。根据经验值,再添加10%的margin(用于总线模块互连线上的功耗),即可以得出系统总线的整体功耗结果。